A Scalable 9σ Additive White Gaussian Noise (AWGN) Generator

The SP1100-SP4000 is fully digital AWGN IP-Core that is scalable to up to 400Gb/s. It

generates white Gaussian noise, which can be used to perform BER Test to extremely

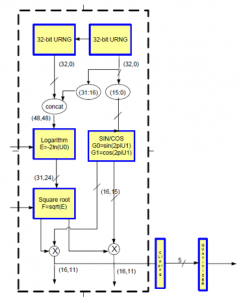

low BER levels (~10-15). The SP1100-SP4000 uses a combination of the Box-Muller algorithm

and the central limit theorem. The Box-Muller algorithm generates a unit normal random

variable via a transformation of two independent random variables that are uniformly

distributed. The outputs of multiple parallel Box-Muller designs are then averaged to

obtain a PDF that is Gaussian to up to 9σ.

The Additive White Gaussian Noise (AWGN) generator is widely used in BER Testing.

The software-based AWGN generator can take several days or several weeks for the BER

curve calculation when reach low bit error rates. Also, the transferring software generated

noise sample to the hardware IP is highly inefficient and it can be a performance

bottleneck.

Hardware-based AWGN noise generator offers the speed of BER by several orders of

magnitude. It can be connected to the designed IP for BERT curve calculation in the

simulation. And also, it can be synthesized and implemented in FPGA with designed IP.

Main Features

- Scalable from 10Gb/s to 400Gb/s @ 300MHz

- Probability desity function (PDF) deviation is in order of 10-4 and σ can reach 10.59

- Based on Box-Muller algorithm

- Period of generated noise sequence is ~ 2^88 = 10^25 samples

- SNR input selection is 16 bit covering from 0.0 dB to 15.9 dB

- Noise is quantized to 16 bits with 5 bits of integer and 11 bits of fraction

- Core returns to initial state upon reset

- Core can hold on and pause then continue the sequence when Enable pin is de-asserted

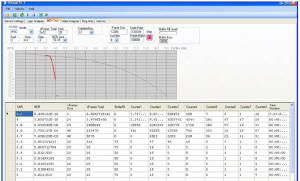

The resulting histogram is shown overlaying the expected Gaussian distribution (log scale is used)

Figure 1 Noise Distribution Curve of AWGN

Figure 2 Block Diagram of AWGN Core

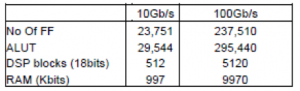

Utilization

The table on the right shows the resource utilization of the SP1100 core (10Gb/s). The core was synthesized onto an Altera StratixV FPGA with maximum operating frequency of 250MHz.

Higher data rate version such as SP4000, which can reach up to 400G/s in typical 16nm ASIC process.

Typical applications

- FEC performance

- Bit Error Rate Testing

Design Example

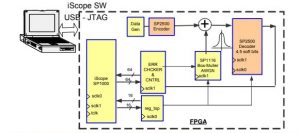

The iScope BER Testing integrated with AWGN can be performed to evaluate the performance of FEC or test the BER of any communication channel such as SERDES or wireless, forward error correction (FEC) bit error rate (BER) testing is performed by modulating data pattern with Additive White Gaussian Noise (AWGN), and feeding it into the system, then calculating the BER based on the number errors the system corrected. There are two mechanisms in the iScope to perform BER test, either using the SW utility provided with the iScope SW, or using a Plug-In hardware accelerated noise generator. The HW accelerated noise generator, is used when it is required to perform tests at extremely low BER (down to BER 10-15 and below).

Figure 3 BER Test Setup for SD-FEC using AWGN and Iscope FPGA Validation Platform

Figure 4 BER Plot of the SD-FEC performance validation using Iscope and AWGN