The Precise-ITC CGPCS IP core is an innovative implementation of the 802.3ba 100G PCS with an optional 802.3bj forward error correction (FEC) layer. It is an efficient solution for challenging 100G Ethernet applications.

The CGPCS core interfaces with the CGMII and PMA. It can connect to a 100G MAC, such as the Precise-ITC CGMAC, through the CGMII to form a complete PCS layer function for Ethernet. The core also provides an interface for connection to an OTN layer. The CGPCS core performs the 66/64B encoding/decoding, alignment marker insertion/removal, PCS block sync, lane alignment, lane deskew and lane reorder functions. It is fully compliant to ITU G.709 Annex E, IEEE 802.3-2012 Clause 82, IEEE 802.3bj-2014, and IEEE 802.3cd-D3.x.

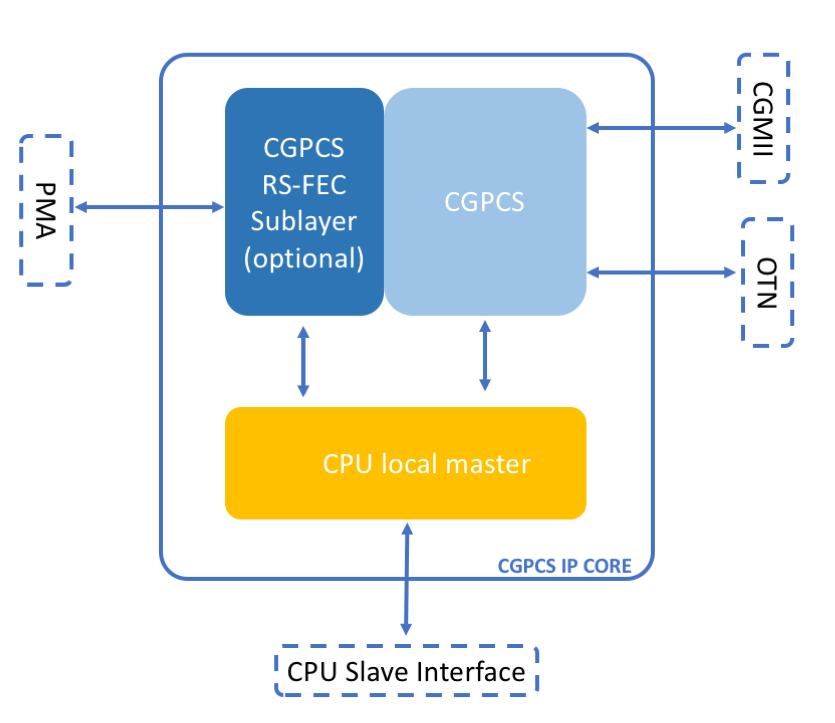

The following shows a block diagram of the CGPCS IP core.

The CDPCS IP core contains the following major functional modules:

- CGPCS – performs the PCS-R (66/64 coding), PCS block sync, alignment lock and deskew, and reorder functions of the IEEE 802.3-2012 Clause 82.

2. CGPCS RS-FEC layer (OPTIONAL) – adds 257B transcoding, Reed Solomon Encoding/Decoding, symbol distribution to PMA lanes

3. CPU local master – it acts as CPU slave to an external CPU for register access and it also acts as a register bridge.

4. MDIO slave – it provides an alternative register access for the core. (Optional)

- TX 64/66B encode

- TX Scrambling enable/disable

- TX IDLE removal and AM (Alignment Marker) insertion

- RX Block synchronization

- RX Alignment lock and Lane Deskew

- RX Lane Reorder

- RX 64/66B decode

- RX Descrambling enable/disable

- RX IDLE insertion and AM (Alignment Marker) deletion

- RX Performance Monitoring and Statistics

- 64/66B decode error

- BER count on sync bits

- HI_BER error

- AM lock error count

- BLOCK_LOCK

- AM_LOCK

- AM BIP errors and counts

- MDIO slave to access PCS MDIO registers in additional to generic CPU interface

- TX 257B transcoding

- TX Alignment marker mapping and insertion

- TX Reed Solomon encoding

- TX FEC parity insertion and Symbol distribution to PMA lanes

- RX Alignment Lock and Deskew

- RX Lane Reorder

- RX Reed Solomon decoding

- RX AM Removal

- RX Reverse 257B Transcoding

- RX Performance Monitoring and Statistics

- Symbol errors

- Corrected codewords

- Uncorrected codewords

Standard Compliance

- IEEE 802.3-2018

- IEEE 802.3cd-D3.x

- ITU-T REC-G.709/Y.1331-02/2012