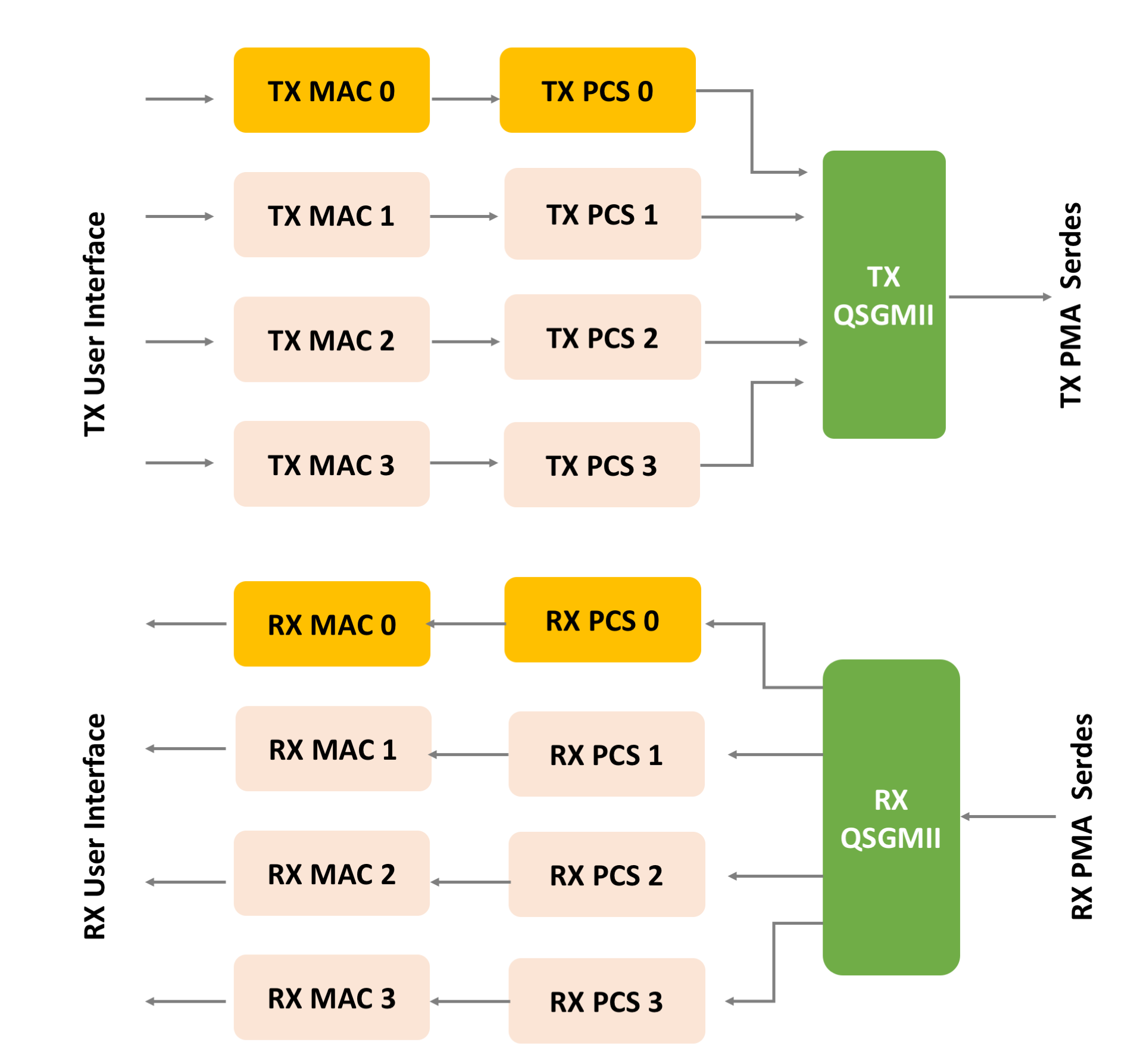

The fully integrated 5G QSGMII, 2.5G/1.25G SGMII and 1000BASE-X Physical Coding Sublayer (PCS-X) and Media Access Controller (MAC) core for Ethernet applications is complaint with IEEE 802.3 standard and QSGMII and SGMII specifications. The interface to the PMA supports a single channel Tri mode bi-directional, serial interface. The PCS sublayer supports 8B10B encoding (QSGMII/SGMII/1000BASE-X). This Tri-Mode Core is configurable through software register.

The West-bound interface from the MAC provides a configurable 32-bit system interface.

The East-bound interface performs the mapping of transmit and receive data streams (at the PMA layer) to the on-chip SERDES.

Figure 1 QSGMII/SGMII/1000BASE-X MAC Block Diagram

Benefits

- Proven IP reduces development time and risk

- Support 5Gbps, 2.5Gbps and 1.25Gbps serdes interfaces

- Support QSGMII, SGMII and 1000BASE-X 8B10B PCS encoding

- Support 4 or 1 channel operations

- Off-the-shelf, proven technology implementation in FPGAs and ASIC SOC

- Tested and interoperability-proven

Features

- Integrated MAC and PCS for area efficiency

- Fully compatible with IEEE802.3 2015 standard, QSGMII specification 1.2, and SGMII specification 1.6 Standard

- Super low latency with minimized fixed and variable delay for network efficiency.

- Supports 1588v2 1-step and 2-step time stamps and full error handling

- Supports 802.1Qbb priority flow control (PFC)